EDA Metadata

The EDAM (EDA Metadata) API is a data structure with the intention to describe all input parameters that an EDA tool will need to run synthesis or build a simulation model from a set of HDL files. The data described in EDAM is tool-agnostic, with the option to supply tool-specific parameters when required. The data structure itself is a tree structure with lists and dictionaries using simple data types as strings and integers for the actual values, and is suitable for (de)serialization with YAML or JSON.

Most keys are optional. The ones which are required are marked accordingly

Field Name |

Type |

Description |

|---|---|---|

dependencies |

Dict of Dependency |

Direct dependencies of each core that is contained in the EDAM. |

files |

List of File |

Contains all the HDL source files, constraint files, vendor IP description files, memory initialization files etc. for the project. |

flow_options |

A dictionary of tool- and flow-specific options. Used by the Flow API |

|

hooks |

A dictionary of extra commands to execute at various stages of the project build/run. |

|

name |

String |

Required Name of the project |

parameters |

Dict of Parameter |

Specifies build- and run-time parameters, such as plusargs, VHDL generics, Verilog defines etc. |

tool_options |

A dictionary of tool-specific options. Used by the legacy Tool API |

|

toplevel |

List of String |

Toplevel module(s) for the project. |

version |

String |

EDAM Version of the file. |

vpi |

List of VPI |

VPI modules to build for the project. |

Dependency

An EDAM description is typically composed from multiple cores that have been combined to a larger project. In some cases it can be useful for Edalize flows or tools to be aware of the relation between these cores so that they can recreate the dependency tree. Each Dependency entry contains a list of other cores on which it has a direct dependency.

Example dict of Dependency entries where ::corescore:0 is the toplevel core which depends on ::servant:1.0.0, ::serving:1.0 and ::verilog-axis:0-r2. Both servant and serving in turn depend on serv:

dependencies:

::corescore:0:

- ::servant:1.0.0

- ::serving:0

- ::verilog-axis:0-r2

::serv:1.0.0-r1: []

::servant:1.0.0:

- ::serv:1.0.0-r1

::serving:0:

- ::serv:1.0.0-r1

::verilog-axis:0-r2: []

File

A file has a name, which is the absolute path or the relative path to the working directory. It also has a type, which describes the intended usage of the file. Different EDA tools handle different subsets of files and are expected to ignore files that are not applicable to them, but might issue a warning. By specifying user as the file type, the backends will explicitly ignore the file. The valid file types are based on the IP-XACT 2014 standard, with some additional file types added. The file types not covered by IP-XACT are listed below

QIP : Intel Quartus IP file

UCF : Xilinx ISE constraint file

verilogSource-2005 : Verilog 200 source

vhdlSource-2008 : VHDL 2008 source

xci : Xilinx Vivado IP file

xdc : Xilinx Vivado constraint file

Field Name |

Type |

Description |

|---|---|---|

name |

String |

Required File name with (absolute or relative) path |

file_type |

String |

Required File type |

is_include_file |

Bool |

Indicates if this file should be treated as an include file (default false) |

include_path |

String |

When is_include_file is true, the directory containing the file will be added to the include path. include_path allows setting an explicit directory to use instead |

logical_name |

String |

Logical name (e.g. VHDL/SystemVerilog library) of the file |

Flow options

The flow API consists of two layers. The flow defines how different tools are interconnected to perform a task. The topology of the flows can be very different. A simulation flow might consist of a single simulation tool. An FPGA flow might be built up from a synthesis tool followed by a place & route tool and finally some tool to convert into a device-specific FPGA image (bitstream). A gate-level simulation flow could be created with a synthesis tool feeding its output into a simulator.

This also means that configuring the flow consists of two types of options. The flow options listed for each flow below defines the topology. Depending on which tools that get pulled into the flow graph, additional tool-specific flow options becomes available as well. In addition, some tool-specific options might be hardcoded by the flow. If e.g. yosys is used in the Vivado flow, the architecture will always be set to xilinx and the output format will always be edf since that’s what Vivado expects for its post-synthesis activities. Below is listed the flow options for each flow as well as the tool options for each tool. In order to programatically see what options are available for a specific flow configuration, first run get_flow_options() to get the available flow options. Assign values to any flow options of interest and then run get_tool_options(assigned_flow_options) with a dict containing the flow options and their values to see what tool options are available for this particular flow configuration.

The global flow options and options for each tool both goes into the flow_options section in the EDAM description.

Efinity flow

Efinix Efinity FPGA toolchain

![digraph G {

"$project.bit" [shape=box,style=filled]

frontends -> efinity;

efinity -> "$project.bit";

}](../_images/graphviz-30d1bdd2f86201e8432590dd84f320f98ccb8a79.png)

Field Name |

Type |

Description |

|---|---|---|

frontends |

List of str |

Tools to run before main flow |

F4pga flow

Edalize back-end implementation of F4PGA (Free and Open-Source Flow For FPGAs)

![digraph G {

yosyseblif [label="yosys\noutput_format=eblif"]

yosysjson [label="yosys\noutput_format=json"]

"$project.bit" [shape=box,style=filled]

frontends -> yosysjson[label="pnr==nextpnr "];

frontends -> yosyseblif[label="pnr==vpr "];

yosysjson -> nextpnr;

yosyseblif -> vpr;

vpr -> genfasm;

genfasm -> xcfasm;

xcfasm -> "$project.bit";

}](../_images/graphviz-1f235efee1ee61048e0fecb59ded97b5e288702d.png)

Field Name |

Type |

Description |

|---|---|---|

device |

str |

Example: ‘artix7’ |

part |

str |

Example: ‘xc7a35tcpg236-1’ |

chip |

str |

Example: ‘xc7a50t_test’ |

arch |

str |

Targeting architecture for Yosys. Currently supported is ‘xilinx’ and that is the default if none specified. |

pnr |

str |

Place and route tool. Valid options are ‘vpr’/’vtr’ and ‘nextpnr’. Defaults to VPR. |

vpr_options |

list |

Options to VPR, if the standard F4PGA values are not sufficient |

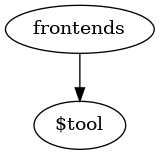

Generic flow

Run an arbitrary tool

![digraph G {

"?" [shape=box,style=filled]

frontends -> "$tool";

"$tool" -> "?";

}](../_images/graphviz-110e48144c84be6fe1ac347ad616db6615955a34.png)

Field Name |

Type |

Description |

|---|---|---|

frontends |

List of str |

Tools to run before main flow |

tool |

str |

Select tool |

Gls flow

Run a gate-level simulation

![digraph G {

"model" [shape=box,style=filled,label="Simulation model"]

frontends -> "$synth";

"$synth" -> "$sim";

"$sim" -> "model";

}](../_images/graphviz-2464a9f6dd013b7b36678f0b7b7ea929d4d42e29.png)

Field Name |

Type |

Description |

|---|---|---|

frontends |

List of str |

Tools to run before main flow |

synth |

str |

Synthesis tool |

synth_top |

str |

Top module of synthesised part of the design |

sim |

str |

Simulator |

Icestorm flow

Open source toolchain for Lattice iCE40 FPGAs. Uses yosys for synthesis and nextpnr for Place & Route

![digraph G {

"$project.bit" [shape=box,style=filled]

"$project.json" [shape=box,style=filled]

yosys [label="yosys\narch=ice40\noutput_format=json"]

nextpnr [label="nextpnr\narch=ice40"]

frontends -> yosys;

yosys -> nextpnr;

yosys -> "$project.json" [label="pnr==none"];

nextpnr -> icetime;

nextpnr -> icebox_stat;

nextpnr -> icepack;

icepack -> "$project.bit";

}](../_images/graphviz-f5602d577a4e4801390732dbee142d252fc20bd3.png)

Field Name |

Type |

Description |

|---|---|---|

frontends |

List of str |

Tools to run before yosys (e.g. sv2v) |

pnr |

str |

Select Place & Route tool. Legal values are next for nextpnr or none to only perform synthesis. Default is next |

Lint flow

Run a linter tool on the design

Field Name |

Type |

Description |

|---|---|---|

frontends |

List of str |

Tools to run before main flow |

tool |

str |

Select tool |

Sim flow

Run a simulation

![digraph G {

"model" [shape=box,style=filled,label="Simulation model"]

frontends -> "$tool";

"$tool" -> "model";

}](../_images/graphviz-d688839afaba35444f7549436fae472f4f7f3467.png)

Field Name |

Type |

Description |

|---|---|---|

frontends |

List of str |

Tools to run before main flow |

tool |

str |

Select tool |

cocotb_module |

str |

Cocotb test python module. (Enables Cocotb simulations) |

Vivado flow

The Vivado flow executes AMD Vivado to create a bitstream and optionally program a board. Yosys can be used for synthesis by setting the synth option accordingly

![digraph G {

yosys [label="yosys\narch=xilinx\noutput_format=edif"]

vpnr [label="vivado\nsynth=none"]

"$project.bit" [shape=box,style=filled]

"$project.v" [shape=box,style=filled]

frontends -> yosys[label="synth==yosys "];

frontends -> "vivado"[label="synth!=yosys"];

yosys -> "vpnr";

vivado -> "$project.v"[label="pnr==none"];

vivado -> "$project.bit"[label="pnr!=none"];

"vpnr" -> "$project.bit";

}](../_images/graphviz-203dfbe5e229b1a6e497ccd6153945233b3489fd.png)

Field Name |

Type |

Description |

|---|---|---|

frontends |

List of str |

Tools to run before Vivado (e.g. sv2v) |

pgm |

bool |

Program board after bitstream is complete |

pnr |

str |

Select Place & Route tool. |

synth |

str |

Synthesis tool. Allowed values are vivado (default) and yosys. |

Vpr flow

VPR is an open source academic CAD tool designed for the exploration of new FPGA architectures and CAD algorithms, at the packing, placement and routing phases of the CAD flow

![digraph G {

yosysblif [label="yosys\noutput_format=blif"]

"$project.analysis" [shape=box,style=filled]

frontends -> yosysblif;

yosysblif -> vpr;

vpr -> "$project.analysis";

}](../_images/graphviz-5a515f6f6fdc1d73ddc32093d28b83a6ba54522d.png)

Field Name |

Type |

Description |

|---|---|---|

Efinity tool

Efinity Backend.

The Efinity backend executes Efinity to build systems and program the FPGA

Field Name |

Type |

Description |

|---|---|---|

family |

str |

FPGA family. Accepted is Trion and Titanium (default) |

part |

str |

FPGA part number (e.g. Ti180M484) |

timing |

str |

Speed grade (e.g. C4) |

Ghdl tool

GHDL is an open source VHDL simulator, which fully supports IEEE 1076-1987, IEEE 1076-1993, IEE 1076-2002 and partially the 1076-2008 version of VHDL

Field Name |

Type |

Description |

|---|---|---|

mode |

str |

Select operation mode. verilog to create verilog, sim to run simulation. Default sim |

Icarus tool

Icarus Verilog is a Verilog simulation and synthesis tool. It operates as a compiler, compiling source code written in Verilog (IEEE-1364) into some target format

Field Name |

Type |

Description |

|---|---|---|

timescale |

str |

Default timescale |

iverilog_options |

str |

Additional options for iverilog |

vvp_options |

str |

Additional options for vvp |

Icepack tool

Generate binary image for iCE40 FPGAs

Field Name |

Type |

Description |

|---|---|---|

icepack_options |

List of str |

Additional options for icepack |

Icetime tool

Static timing analysis for iCE40 FPGAs

Field Name |

Type |

Description |

|---|---|---|

icetime_options |

List of str |

Additional options for icetime |

Nextpnr tool

A portable FPGA place and route tool

Field Name |

Type |

Description |

|---|---|---|

arch |

str |

Architecture for nextpnr |

nextpnr_options |

List of str |

Additional options for nextpnr |

Sandpipersaas tool

SandPiper SaaS Edition runs Redwood EDA’s SandPiper™ TL-Verilog compiler as a microservice in the cloud to support low-overhead and zero-cost open-source development using commercial-grade capabilities

Field Name |

Type |

Description |

|---|---|---|

sandpiper_saas |

str |

Optional: Additional options for sandpiper-saas |

sandpiper_jar |

str |

Optional: Additional options for sandpiper_jar |

output_file |

str |

Optional(Recommended): Name of the output Verilog/System Verilog file (Must contain .v or .sv). Defaults to proj_name_tlv.v |

output_dir |

str |

Optional: Path to the output directory, Defaults to the current directory` |

endpoint |

str |

Compile service endpoint |

includes |

str |

Optional: List of include files to be used during compilation |

Surelog tool

SystemVerilog 2017 Pre-processor, Parser, Elaborator, UHDM Compiler

Field Name |

Type |

Description |

|---|---|---|

surelog_options |

List of str |

Additional options for surelog |

Sv2v tool

SystemVerilog to Verilog conversion

Field Name |

Type |

Description |

|---|---|---|

sv2v_options |

List of str |

Additional options for sv2v |

Verilator tool

Verilator, the fastest Verilog/SystemVerilog simulator

Field Name |

Type |

Description |

|---|---|---|

exe |

str |

Controls whether to create an executable. Set to ‘false’ when something else will do the final linking |

make_options |

str |

Additional arguments passed to make when compiling the simulation. This is commonly used to set OPT/OPT_FAST/OPT_SLOW. |

mode |

str |

Select compilation mode. Use none for no compilation mode. Legal values are binary, cc, dpi-hdr-only, lint-only, none, preprocess-only, sc, xml-only. See Verilator documentation for function: https://veripool.org/guide/latest/exe_verilator.html |

gen-xml |

bool |

Generate XML output |

gen-dpi-hdr |

bool |

Generate DPI header output |

gen-preprocess |

bool |

Generate preprocessor output |

verilator_options |

List of str |

Additional options for verilator |

Vivado tool

Vivado Backend.

A core (usually the system core) can add the following files:

Standard design sources

Constraints: Supply xdc files with file_type=xdc or unmanaged constraints with file_type SDC

IP: Supply the IP core xci file with file_type=xci and other files (like .prj) as file_type=user

Field Name |

Type |

Description |

|---|---|---|

part |

str |

FPGA part number (e.g. xc7a35tcsg324-1) |

synth |

str |

Synthesis tool. Allowed values are vivado or none. |

board_part |

str |

Board part number (e.g. xilinx.com:kc705:part0:0.9) |

board_repo_paths |

str |

Board repository paths. A list of paths to search for board files. |

pnr |

str |

P&R tool. Allowed values are vivado (default) and none (to just run synthesis) |

jobs |

int |

Number of jobs. Useful for parallelizing OOC (Out Of Context) syntheses. |

jtag_freq |

int |

The frequency for jtag communication |

source_mgmt_mode |

str |

Source managment mode. Allowed values are None (unmanaged, default), DisplayOnly (automatically update sources) and All (automatically update sources and compile order) |

hw_target |

str |

A pattern matching a board identifier. Refer to the Vivado documentation for |

Vpr tool

VPR tool Backend

The VPR backend performs Packing, Placement, Routing & Timing Analysis.

Field Name |

Type |

Description |

|---|---|---|

arch_xml |

str |

Path to target architecture in XML format |

generate_constraints |

list |

A list of values used to generate constraints at the place stage (used by F4PGA flow) |

vpr_options |

List of str |

Additional options for VPR. |

Yosys tool

Open source synthesis tool targeting many different FPGAs

Field Name |

Type |

Description |

|---|---|---|

arch |

str |

Target architecture. Legal values are xilinx, ice40 and ecp5 |

output_format |

str |

Output file format. Legal values are json, edif, blif, verilog |

yosys_template |

str |

TCL template file to use instead of default template |

f4pga_synth_part_file |

str |

The JSON part file used for Yosys synthesis |

yosys_synth_options |

List of str |

Additional options for the synth command |

Hook

Hooks are scripts that can be registered to execute during various phases of Edalize. The Hook structure contains a key for each of the four defined stages, and the value of each key is a list of Script to be executed.

The four defined stages are

Key |

Description |

|---|---|

pre_build |

Executed before calling build |

post_build |

Executed after calling build |

pre_run |

Executed before calling run |

post_run |

Executed after calling run |

Script

Field Name |

Type |

Description |

|---|---|---|

cmd |

List of String |

Command to execute |

env |

Dict of String |

Additional environment variables to set before launching script |

name |

String |

User-friendly name of the script |

Parameter

A parameter is used for build- and run-time parameters, such as Verilog plusargs, VHDL generics, Verilog defines, Verilog parameters or any extra command-line options that should be sent to the simulation model. Different tools support different subsets of parameters. The list below describes valid parameter types

cmdlinearg : Command-line argument to be sent to a running simulation model

generic : VHDL generic to be set at elaboration-time

plusarg : Verilog plusarg to be set at run-time

vlogdefine : Verilog define to be set at compile-time

vlogparam : Verilog toplevel parameter to be set at compile-time

Field Name |

Type |

Description |

|---|---|---|

datatype |

String |

Required Data type of the parameter. Valid values are bool, file, int, str. file is similar to str, but the value is treated as a path and converted to an absolute path |

default |

Specified by datatype |

Default value to use if user does not provide a value during the configure or run stages |

description |

String |

User-friendly description of the parameter |

paramtype |

String |

Required Type of parameter. Valid values are cmdlinearg, generic, plusarg, vlogparam, vlogdefine |

Tool options

Tool options are used to set tool-specific options. Each key corresponds to a specific EDA tool.

Note This section is only used by the legacy Tool API

Field Name |

Type |

Description |

|---|---|---|

apicula |

Apicula-specific options |

|

ascentlint |

Ascentlint-specific options |

|

design_compiler |

Design_compiler-specific options |

|

diamond |

Diamond-specific options |

|

f4pga |

F4pga-specific options |

|

gatemate |

Gatemate-specific options |

|

genus |

Genus-specific options |

|

ghdl |

Ghdl-specific options |

|

icarus |

Icarus-specific options |

|

icestorm |

Icestorm-specific options |

|

ise |

Ise-specific options |

|

isim |

Isim-specific options |

|

libero |

Libero-specific options |

|

mistral |

Mistral-specific options |

|

modelsim |

Modelsim-specific options |

|

morty |

Morty-specific options |

|

nextpnr |

Nextpnr-specific options |

|

openfpga |

Openfpga-specific options |

|

openlane |

Openlane-specific options |

|

openroad |

Openroad-specific options |

|

oxide |

Oxide-specific options |

|

quartus |

Quartus-specific options |

|

questaformal |

Questaformal-specific options |

|

radiant |

Radiant-specific options |

|

rivierapro |

Rivierapro-specific options |

|

sandpipersaas |

Sandpipersaas-specific options |

|

slang |

Slang-specific options |

|

spyglass |

Spyglass-specific options |

|

symbiflow |

Symbiflow-specific options |

|

symbiyosys |

Symbiyosys-specific options |

|

trellis |

Trellis-specific options |

|

vcs |

Vcs-specific options |

|

veribleformat |

Veribleformat-specific options |

|

veriblelint |

Veriblelint-specific options |

|

verilator |

Verilator-specific options |

|

vivado |

Vivado-specific options |

|

vpr |

Vpr-specific options |

|

vunit |

Vunit-specific options |

|

xcelium |

Xcelium-specific options |

|

xsim |

Xsim-specific options |

|

yosys |

Yosys-specific options |

Apicula backend

Open source toolchain for Gowin FPGAs. Uses yosys for synthesis and nextpnr for Place & Route

Field Name |

Type |

Description |

|---|---|---|

device |

String |

Required device option for nextpnr-gowin and gowin_pack command (e.g. GW1N-LV1QN48C6/I5) |

arch |

String |

Target architecture. Legal values are xilinx, ice40 and ecp5 |

output_format |

String |

Output file format. Legal values are json, edif, blif, verilog |

output_name |

String |

Output file name. [Optional] |

yosys_as_subtool |

bool |

Determines if Yosys is run as a part of bigger toolchain, or as a standalone tool |

makefile_name |

String |

Generated makefile name, defaults to $name.mk |

yosys_template |

String |

TCL template file to use instead of default template |

yosys_synth_options |

List of String |

Additional options for the synth command |

nextpnr_options |

List of String |

Additional options for nextpnr |

Ascentlint backend

Real Intent Ascent Lint backend

Ascent Lint performs static source code analysis on HDL code and checks for common coding errors or coding style violations.

Field Name |

Type |

Description |

|---|---|---|

ascentlint_options |

List of String |

Additional run options for ascentlint |

Design_compiler backend

The design_compiler backend executes Synopsys design_copiler to build a gate-level netlist

Field Name |

Type |

Description |

|---|---|---|

script_dir |

String |

Path to Syopsys scripts (e.g. /home/user/project/synopsys/scripts) |

dc_script |

String |

Name of the synthesis script to run [located in script_dir](e.g. synth.tcl) |

report_dir |

String |

Path to where reports should be stored (e.g. /home/user/project/synopsys/reports) |

target_library |

String |

The Design Compiler target_library |

libs |

String |

Libraries to use in the Design Compiler link_library |

jobs |

Integer |

Number of jobs. Useful for parallelizing syntheses. |

Diamond backend

Backend for Lattice Diamond

Field Name |

Type |

Description |

|---|---|---|

part |

String |

FPGA part number (e.g. LFE5U-45F-6BG381C) |

F4pga backend

F4PGA is an open-source flow for generating bitstreams from verilog/systemverilog code using Yosys and VPR/NextPNR. Currently only supports Xilinx 7-series boards with support for more coming in the future.

Field Name |

Type |

Description |

|---|---|---|

device |

str |

(Required) The device type identifier. Example: ‘artix7’ |

part |

str |

(Required) The FPGA part specifier. Example: ‘xc7a35tcpg236-1’ |

chip |

str |

(Required) The FPGA chip specifier used by F4PGA. Example: ‘xc7a50t_test’ |

arch |

str |

(Optional) The architecture specifier. Currently defaults to xilinx and is thus optional. |

pnr |

str |

(Optional) The name of the place and route tool to use. Defaults to VPR and is thus optional. |

Gatemate backend

backend for CologneChip GateMate.

Field Name |

Type |

Description |

|---|---|---|

device |

String |

Required device option for p_r command (e.g. CCGM1A1) |

arch |

String |

Target architecture. Legal values are xilinx, ice40 and ecp5 |

output_format |

String |

Output file format. Legal values are json, edif, blif, verilog |

output_name |

String |

Output file name. [Optional] |

yosys_as_subtool |

bool |

Determines if Yosys is run as a part of bigger toolchain, or as a standalone tool |

makefile_name |

String |

Generated makefile name, defaults to $name.mk |

yosys_template |

String |

TCL template file to use instead of default template |

p_r_options |

List of string |

Additional option for p_r |

yosys_synth_options |

List of String |

Additional options for the synth command |

Genus backend

The genus backend executes cadence genus to build a gate-level netlist

Field Name |

Type |

Description |

|---|---|---|

script_dir |

String |

Path to Genus scripts (e.g. /home/user/project/genus/scripts) |

genus_script |

String |

Name of the synthesis script to run [located in script_dir](e.g. synth.tcl) |

report_dir |

String |

Path to where reports should be stored (e.g. /home/user/project/genus/reports) |

common_config |

String |

A TCL file to be sourced, defining common project specific variables shared between genus and innovus (Loction of MMMC view, LEFs, DEFs, UPF, Paths, …) |

jobs |

String |

Number of jobs. Useful for parallelizing syntheses. Use “all” to set the number of jobs to the number of cores available. |

Ghdl backend

GHDL is an open source VHDL simulator, which fully supports IEEE 1076-1987, IEEE 1076-1993, IEE 1076-2002 and partially the 1076-2008 version of VHDL

Field Name |

Type |

Description |

|---|---|---|

analyze_options |

List of String |

Options to use for the import (ghdl -i) and make (ghdl -m) phases |

run_options |

List of String |

Options to use for the run (ghdl -r) phase |

Icarus backend

Icarus Verilog is a Verilog simulation and synthesis tool. It operates as a compiler, compiling source code written in Verilog (IEEE-1364) into some target format

Field Name |

Type |

Description |

|---|---|---|

timescale |

String |

Default timescale |

iverilog_options |

List of String |

Additional options for iverilog |

vvp_options |

List of String |

Additional options for vvp |

Icestorm backend

Open source toolchain for Lattice iCE40 FPGAs. Uses yosys for synthesis and arachne-pnr or nextpnr for Place & Route

Field Name |

Type |

Description |

|---|---|---|

pnr |

String |

Select Place & Route tool. Legal values are arachne for Arachne-PNR, next for nextpnr or none to only perform synthesis. Default is next |

arch |

String |

Target architecture. Legal values are xilinx, ice40 and ecp5 |

output_format |

String |

Output file format. Legal values are json, edif, blif, verilog |

output_name |

String |

Output file name. [Optional] |

yosys_as_subtool |

bool |

Determines if Yosys is run as a part of bigger toolchain, or as a standalone tool |

makefile_name |

String |

Generated makefile name, defaults to $name.mk |

yosys_template |

String |

TCL template file to use instead of default template |

arachne_pnr_options |

List of String |

Additional options for Arachnhe PNR |

frontends |

List of String |

fixme |

yosys_synth_options |

List of String |

Additional options for the synth command |

nextpnr_options |

List of String |

Additional options for nextpnr |

Ise backend

Xilinx ISE Design Suite

Field Name |

Type |

Description |

|---|---|---|

family |

String |

FPGA family (e.g. spartan6) |

device |

String |

FPGA device (e.g. xc6slx45) |

package |

String |

FPGA package (e.g. csg324) |

speed |

Integer |

FPGA speed grade (e.g. -2) |

board_device_index |

Integer |

Specifies the FPGA’s device number in the JTAG chain, starting at 1 |

pgm |

String |

Programming tool. Default is ‘none’, set to ‘ise’ to program the FPGA in the run stage. |

Isim backend

Xilinx ISim simulator from ISE design suite

Field Name |

Type |

Description |

|---|---|---|

fuse_options |

List of String |

Additional options for compilation with FUSE |

isim_options |

List of String |

Additional run options for ISim |

Libero backend

The Libero backend supports Microsemi Libero to build systems and program the FPGA

Field Name |

Type |

Description |

|---|---|---|

family |

String |

FPGA family (e.g. PolarFire) |

die |

String |

FPGA device (e.g. MPF300TS) |

package |

String |

FPGA package type (e.g. FCG1152) |

speed |

String |

FPGA speed rating (e.g. -1) |

dievoltage |

String |

FPGA die voltage (e.g. 1.0) |

range |

String |

FPGA temperature range (e.g. IND) |

defiostd |

String |

FPGA default IO std (e.g. “LVCMOS 1.8V”) |

hdl |

String |

Default HDL (e.g. “VERILOG”) |

Mistral backend

Project mistral enables a fully open-source flow for Cyclone V FPGAs using Yosys for Verilog synthesis and nextpnr for place and route

Field Name |

Type |

Description |

|---|---|---|

device |

String |

Required device option for nextpnr-mistral command (e.g. 5CEFA5F23I7) |

arch |

String |

Target architecture. Legal values are xilinx, ice40 and ecp5 |

output_format |

String |

Output file format. Legal values are json, edif, blif, verilog |

output_name |

String |

Output file name. [Optional] |

yosys_as_subtool |

bool |

Determines if Yosys is run as a part of bigger toolchain, or as a standalone tool |

makefile_name |

String |

Generated makefile name, defaults to $name.mk |

yosys_template |

String |

TCL template file to use instead of default template |

yosys_synth_options |

List of String |

Additional options for the synth command |

nextpnr_options |

List of String |

Additional options for nextpnr |

Modelsim backend

ModelSim simulator from Mentor Graphics

Field Name |

Type |

Description |

|---|---|---|

compilation_mode |

String |

Common or separate compilation, sep - for separate compilation, common - for common compilation |

vcom_options |

List of String |

Additional options for compilation with vcom |

vlog_options |

List of String |

Additional options for compilation with vlog |

vsim_options |

List of String |

Additional run options for vsim |

Morty backend

Run the (System-) Verilog pickle tool called morty.

Field Name |

Type |

Description |

|---|---|---|

morty_options |

List of String |

Run-time options passed to morty. |

Nextpnr backend

a portable FPGA place and route tool

Field Name |

Type |

Description |

|---|---|---|

nextpnr_options |

List of String |

Additional options for nextpnr |

Openfpga backend

The OpenFPGA backend executes Yosys synthesis tool and VPR place and route. It can target multiple different open-source FPGAs (supported: sofa-chd, sofa-hd, sofa-qlhd, sofa-plus-hd)

Field Name |

Type |

Description |

|---|---|---|

arch |

String |

Target architecture. Legal values are sofa and sofa-plus. |

task_options |

List of String |

Additional options for OpenFPGA task flow execution. |

Openlane backend

Open source flow for ASIC synthesis, placement and routing

Field Name |

Type |

Description |

|---|---|---|

Openroad backend

Open source flow for ASIC synthesis, placement and routing

Field Name |

Type |

Description |

|---|---|---|

flow_path |

String |

Path to OpenROAD-flow-script/flow |

make_target |

String |

make target (default: finish) |

Oxide backend

Project Oxide enables a fully open-source flow for Nexus FPGAs using Yosys for Verilog synthesis and nextpnr for place and route

Field Name |

Type |

Description |

|---|---|---|

device |

String |

Required device option for nextpnr-nexus command (e.g. LIFCL-40-9BG400C) |

arch |

String |

Target architecture. Legal values are xilinx, ice40 and ecp5 |

output_format |

String |

Output file format. Legal values are json, edif, blif, verilog |

output_name |

String |

Output file name. [Optional] |

yosys_as_subtool |

bool |

Determines if Yosys is run as a part of bigger toolchain, or as a standalone tool |

makefile_name |

String |

Generated makefile name, defaults to $name.mk |

yosys_template |

String |

TCL template file to use instead of default template |

yosys_synth_options |

List of String |

Additional options for the synth command |

nextpnr_options |

List of String |

Additional options for nextpnr |

Quartus backend

The Quartus backend supports Intel Quartus Std and Pro editions to build systems and program the FPGA

Field Name |

Type |

Description |

|---|---|---|

family |

String |

FPGA family (e.g. Cyclone V) |

device |

String |

FPGA device (e.g. 5CSXFC6D6F31C8ES) |

cable |

String |

Specifies the FPGA’s JTAG programming cable. Use the tool jtagconfig to determine the available cables. |

board_device_index |

Integer |

Specifies the FPGA’s device number in the JTAG chain. The device index specifies the device where the flash programmer looks for the Nios® II JTAG debug module. JTAG devices are numbered relative to the JTAG chain, starting at 1. Use the tool jtagconfig to determine the index. |

pnr |

String |

P&R tool. Allowed values are quartus (default), dse (to run Design Space Explorer) and none (to just run synthesis) |

pgm |

String |

Programming tool. Default is ‘none’, set to ‘quartus’ to program the FPGA in the run stage. |

dse_options |

List of String |

Options for DSE (Design Space Explorer) |

quartus_options |

List of String |

Additional options for Quartus |

Questaformal backend

Questa Formal from Mentor Graphics

Field Name |

Type |

Description |

|---|---|---|

vcom_options |

List of String |

Additional options for compilation with vcom |

vlog_options |

List of String |

Additional options for compilation with vlog |

qverify_options |

List of String |

Additional run options for qverify |

autocheck_options |

List of String |

Options for Autochecker |

Radiant backend

Backend for Lattice Radiant

Field Name |

Type |

Description |

|---|---|---|

part |

String |

FPGA part number (e.g. LIFCL-40-9BG400C) |

Rivierapro backend

Riviera Pro simulator from Aldec

Field Name |

Type |

Description |

|---|---|---|

compilation_mode |

String |

Common or separate compilation, sep - for separate compilation, common - for common compilation |

vlog_options |

List of String |

Additional options for compilation with vlog |

vsim_options |

List of String |

Additional run options for vsim |

Sandpipersaas backend

SandPiper SaaS Edition runs Redwood EDA’s SandPiper™ TL-Verilog compiler as a microservice in the cloud to support low-overhead and zero-cost open-source development using commercial-grade capabilities.

Field Name |

Type |

Description |

|---|---|---|

sandpiper_saas |

List of String |

Additional options for sandpiper-saas |

sandpiper_jar |

List of String |

Additional options for sandpiper_jar |

output_file |

List of String |

Name of the output Verilog/System Verilog file (Must contain .v or .sv |

output_dir |

List of String |

Optional: Path to the output directory |

endpoint |

List of String |

Compile service endpoint |

includes |

List of String |

List of include files to be used during compilation |

Slang backend

slang is a software library that provides various components for lexing, parsing, type checking, and elaborating SystemVerilog code.

Field Name |

Type |

Description |

|---|---|---|

mode |

List of String |

choose slang to run in either lint mode or preprocess mode |

slang_options |

List of String |

extra options for slang |

Spyglass backend

Synopsys (formerly Atrenta) Spyglass Backend

Spyglass performs static source code analysis on HDL code and checks for common coding errors or coding style violations.

Example snippet of a CAPI2 description file

spyglass:

methodology: "GuideWare/latest/block/rtl_handoff"

goals:

- lint/lint_rtl

spyglass_options:

# prevent error SYNTH_5273 on generic RAM descriptions

- handlememory yes

rule_parameters:

# Allow localparam to be used in case labels (e.g. in state machines)

- handle_static_caselabels yes

Field Name |

Type |

Description |

|---|---|---|

methodology |

String |

|

goals |

List of String |

|

spyglass_options |

List of String |

|

rule_parameters |

List of String |

Symbiflow backend

The Symbiflow backend executes Yosys sythesis tool and VPR/Nextpnr place and route. It can target multiple different FPGA vendors

Field Name |

Type |

Description |

|---|---|---|

arch |

String |

Target architecture. Legal values are xilinx and fpga_interchange (this is relevant only for Nextpnr variant). |

package |

String |

FPGA chip package (e.g. clg400-1) |

part |

String |

FPGA part type (e.g. xc7a50t) |

vendor |

String |

Target architecture. Currently only “xilinx” is supported |

pnr |

String |

Place and Route tool. Currently only “vpr”/”vtr” and “nextpnr” are supported |

vpr_options |

String |

Additional options for VPR tool. If not used, default options for the tool will be used |

nextpnr_options |

String |

Additional options for Nextpnr tool. If not used, default options for the tool will be used |

Symbiyosys backend

SymbiYosys formal verification wrapper for Yosys

Field Name |

Type |

Description |

|---|---|---|

tasknames |

List of String |

A list of the .sby file’s tasks to run. Passed on the sby command line. |

Trellis backend

Project Trellis enables a fully open-source flow for ECP5 FPGAs using Yosys for Verilog synthesis and nextpnr for place and route

Field Name |

Type |

Description |

|---|---|---|

arch |

String |

Target architecture. Legal values are xilinx, ice40 and ecp5 |

output_format |

String |

Output file format. Legal values are json, edif, blif, verilog |

output_name |

String |

Output file name. [Optional] |

yosys_as_subtool |

bool |

Determines if Yosys is run as a part of bigger toolchain, or as a standalone tool |

makefile_name |

String |

Generated makefile name, defaults to $name.mk |

yosys_template |

String |

TCL template file to use instead of default template |

yosys_synth_options |

List of String |

Additional options for the synth command |

nextpnr_options |

List of String |

Additional options for nextpnr |

Vcs backend

Synopsys VCS Backend

VCS is one of the “Big 3” simulators.

Example snippet of a CAPI2 description file for VCS:

vcs:

vcs_options:

# Compile-time options passed to the vcs command

- -debug_access+pp

- -debug_access+all

run_options:

# Run-time options passed to the simulation itself

- -licqueue

Field Name |

Type |

Description |

|---|---|---|

vcs_options |

List of String |

|

run_options |

List of String |

Veribleformat backend

Verible format backend (verible-verilog-format)

Field Name |

Type |

Description |

|---|---|---|

verible_format_args |

List of String |

Extra command line arguments passed to the Verible tool |

Veriblelint backend

Verible lint backend (verible-verilog-lint)

Field Name |

Type |

Description |

|---|---|---|

ruleset |

String |

Ruleset: [default|all|none] |

verible_lint_args |

List of String |

Extra command line arguments passed to the Verible tool |

rules |

List of String |

What rules to use. Prefix a rule name with “-” to disable it. |

Verilator backend

Verilator is the fastest free Verilog HDL simulator, and outperforms most commercial simulators

Field Name |

Type |

Description |

|---|---|---|

mode |

String |

Select compilation mode. Legal values are binary, cc, dpi-hdr-only, lint-only, none, preprocess-only, sc, xml-only. See Verilator documentation for function: https://veripool.org/guide/latest/exe_verilator.html |

cli_parser |

String |

Deprecated: Use run_options instead : Select whether FuseSoC should handle command-line arguments (managed) or if they should be passed directly to the verilated model (raw). Default is managed |

exe |

String |

Controls whether to create an executable. Set to ‘false’ when something else will do the final linking |

gen-xml |

bool |

Generate XML output |

gen-dpi-hdr |

bool |

Generate DPI header output |

gen-preprocess |

bool |

Generate preprocessor output |

libs |

List of String |

Extra libraries for the verilated model to link against |

verilator_options |

List of String |

Additional options for verilator |

make_options |

List of String |

Additional arguments passed to make when compiling the simulation. This is commonly used to set OPT/OPT_FAST/OPT_SLOW. |

run_options |

List of String |

Additional arguments directly passed to the verilated model |

Vivado backend

The Vivado backend executes Xilinx Vivado to build systems and program the FPGA

Field Name |

Type |

Description |

|---|---|---|

part |

String |

FPGA part number (e.g. xc7a35tcsg324-1) |

board_part |

String |

Board part number (e.g. xilinx.com:kc705:part0:0.9) |

synth |

String |

Synthesis tool. Allowed values are vivado (default) and yosys. |

pnr |

String |

P&R tool. Allowed values are vivado (default) and none (to just run synthesis) |

pgm |

String |

Programming tool. Default is none, set to ‘vivado’ to program the FPGA in the run stage. |

jobs |

Integer |

Number of jobs. Useful for parallelizing OOC (Out Of Context) syntheses. |

jtag_freq |

Integer |

The frequency for jtag communication |

source_mgmt_mode |

String |

Source managment mode. Allowed values are None (unmanaged, default), DisplayOnly (automatically update sources) and All (automatically update sources and compile order) |

hw_target |

Description |

A pattern matching a board identifier. Refer to the Vivado documentation for |

frontends |

String |

|

board_repo_paths |

List of String |

Board repository paths. A list of paths to search for board files. |

Vpr backend

The VPR backend performs Packing, Placement, Routing & Timing Analysis.

Field Name |

Type |

Description |

|---|---|---|

arch_xml |

String |

Path to target architecture. |

vpr_options |

String |

Additional options for VPR. |

Vunit backend

VUnit testing framework

Field Name |

Type |

Description |

|---|---|---|

vunit_runner |

String |

Name of the Python file exporting a “VUnitRunner” class that is used to configure and execute test |

add_libraries |

List of String |

A list of framework libraries to add. Allowed values include “array_util”, “com”, “json4hdl”, “osvvm”, “random”, “verification_components” |

vunit_options |

List of String |

Options to pass to the VUnit test runner |

Xcelium backend

Xcelium simulator from Cadence Design Systems

Field Name |

Type |

Description |

|---|---|---|

xmvhdl_options |

List of String |

Additional options for compilation with xmvhdl |

xmvlog_options |

List of String |

Additional options for compilation with xmvlog |

xmsim_options |

List of String |

Additional run options for xmsim |

xrun_options |

List of String |

Additional run options for xrun |

Xsim backend

XSim simulator from the Xilinx Vivado suite

Field Name |

Type |

Description |

|---|---|---|

compilation_mode |

String |

Common or separate compilation, sep - for separate compilation, common - for common compilation |

xelab_options |

List of String |

Additional options for compilation with xelab |

xsim_options |

List of String |

Additional run options for XSim |

Yosys backend

Open source synthesis tool targeting many different FPGAs

Field Name |

Type |

Description |

|---|---|---|

arch |

String |

Target architecture. Legal values are xilinx, ice40 and ecp5 |

output_format |

String |

Output file format. Legal values are json, edif, blif, verilog |

output_name |

String |

Output file name. [Optional] |

yosys_as_subtool |

bool |

Determines if Yosys is run as a part of bigger toolchain, or as a standalone tool |

makefile_name |

String |

Generated makefile name, defaults to $name.mk |

yosys_template |

String |

TCL template file to use instead of default template |

yosys_synth_options |

List of String |

Additional options for the synth command |

VPI

Each Vpi object contains information on how to build the corresponding VPI library

Field Name |

Type |

Description |

|---|---|---|

include_dirs |

List of String |

Extra include directories |

libs |

List of String |

Extra libraries |

name |

String |

Name of VPI library |

src_files |

List of String |

Source files for VPI library |